Logic with Wires: New Computing Direction Leveraging Interconnect Crosstalks

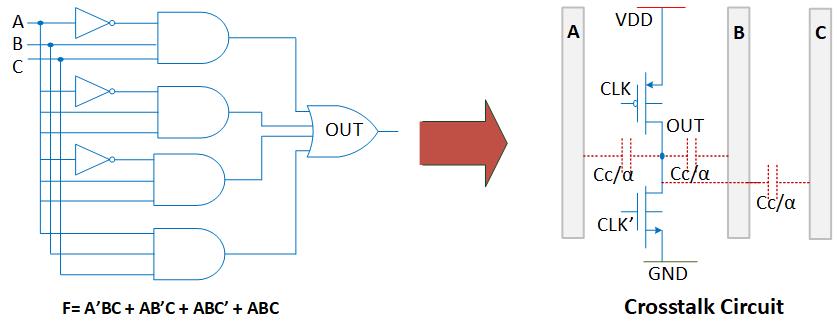

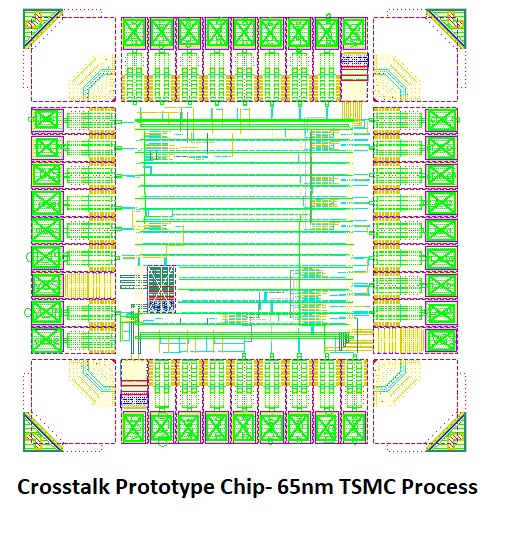

Device, interconnect scaling and interconnection bottleneck are among the major challenges for CMOS scaling. Furhtermore, signal integrity issues like crosstalk- leakage of charge between capacitively coupled nets among neighboring signal lines, is becoming inexorable. We propose to astutely turn this detrimental effect into an advantage by engineering the interference among signal lines. Our proposal can potentially solve scaling challenges by reducing device and interconnect scaling requirements while complying with existing manufacturing paradigm. Central to our approach is the deterministic emulation of aggressor-victim scenarios in metal lines to achieve logic computation. As a result of input transitions on the aggressor nets, summation of aggressor nets charges is introduced on the victim net. The summation signal on victim net serve as outputs for logic gate, or used to control a pass transistor to get desired logic output. Depending on the boolean logic being computed, this sum of charges seen by victim net is controlled primarily by engineering the capacitance between aggressors and victims and by synchronous clocking. We have implemented all basic gates including NAND, NOR, AND, OR and XOR, and arithmetic circuits following this principle. Our results indicate huge potentials for compact and low-power computing using the proposed approach.

Key advantages of this fabric are-

- Computing dependent on interference between interconnects and not device switching — deviceless computing

- Denser, faster and more power efficient compared to CMOS

- Scalable, since scalability depends on circuit integration

- Ability to integrate in 3-D

- Uses existing CAD and fabrication infrastructure

- Uses Junctionless transistors — more radiation and high power microwave tolerant

Current research areas are-

- Investigation of coupling capacitance between different elements in VLSI circuits through RC extraction from circuit layouts

- Capacitance engineering by manipulating materials, structures and circuit components

- Logic decomposition to take advantage of crosstalk phenomenon

- Automated Crosstalk friendly circuit extraction and usage of existing CMOS CAD tools

- Simulation and benchmarking of large-scale circuits

- TCAD simulation of nanostructures to take advantage of Crosstalk

- Analog Crosstalk Circuit design

- Biomedical electronics using Analog Crosstalk

- High Power Microwave tolerant Circuit design