Fine Grained Transistor-Level 3-D Integration

Migration of traditional 2-D CMOS to 3-D has been elusive, since inherent customization requirements of CMOS circuits are not compatible for fine-grained 3-D. Partial attempts for 3-D CMOS with die-die and layer-layer stacking show incremental density benefits, but retain same CMOS scaling challenges, and add new constraints. In contrast to CMOS that evolved focusing on device centric mindset, where devices are scaled first, and circuit and layouts are optimized as afterthoughts, our research focus is on a nanoscale fine-grained 3-D integrated circuit fabrics that can provide integrated solutions for all nanoscale technology aspects. Key to our 3-D integration is the design of core fabric components that synergistically help to address device, circuit, connectivity, thermal and manufacturing issues in an integrated 3-D compatible manner.

We are working on two different transistor level 3-D integration approaches using vertical (Skybridge) and horizontal nanowires (SN3D). Skybridge focuses on new device, circuit and integration concepts, whereas SN3D uses 3-D specific CMOS circuit style and integration schemes. Key to both approaches are unique architected fabric components that enable circuit implementation, routing and heat management in 3-D.

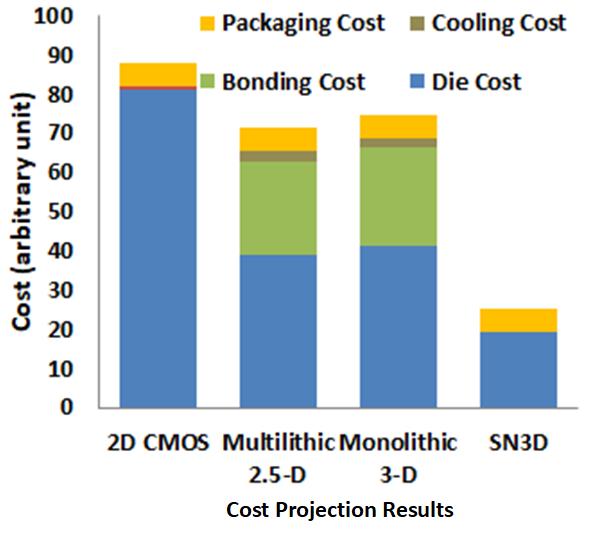

Both designs achieve tremendous benefits compared to state-of-the-art CMOS technologies. Our bottom up evaluation method using TCAD Process, Device and HSPICE circuit simulations accounting for process parameters, material properties, nanoscale transport, 3-D circuit style, layout and parasitics reveals 24.6x density and 13.25x performance/watt benefits compared to CMOS for a 4-bit CLA, and 4.6x density, 4.2x active power and 51.2x leakage power benefits with comparable performance for Skybridge RAM in comparison to CMOS SRAM at 16nm.

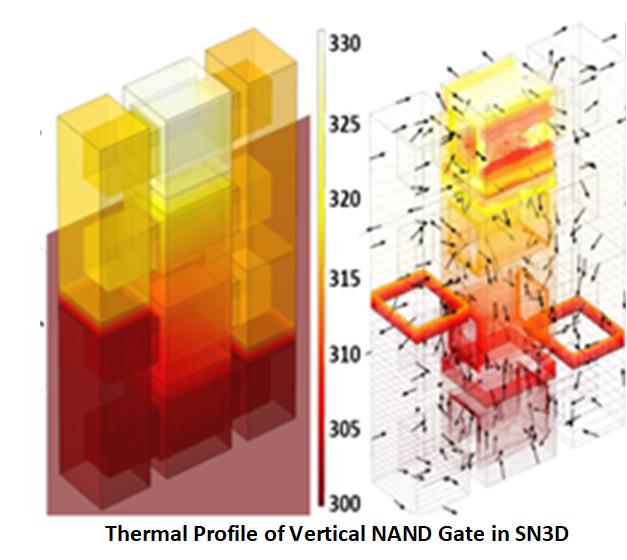

Our thermal evaluation include Finite Element Model based modeling and analysis, analytical modeling of fabric components and HSPICE simulations of 3-D circuits. Our simulation results show effectiveness of architected 3-D heat extraction features in reducing heat to reference temperature.

Current research areas-

- TCAD modeling and simulations of 3-D fabric components

- Behavioral modeling of 3-D components based on TCAD results

- Design rule specification

- Develop CAD flow for 3-D circuits; cell library, layout and routing strategy design and simulation

- Simulation and benchmarking of large-scale circuits vs. CMOS

- Interconnect and cost estimation accounting for process parameters

- Thermal modeling of large circuits and thermal aware circuit design

- Experimental validation of Skybridge and SN3D fabric. To date, we have successfully demonstrated the core device concept, and shown key steps necessary for fabric assembly.